Как выбрать процессор для сервера: рекомендации инженеров ANDPRO

Процессор сервера определяет, какие нагрузки сможет выполнять система: виртуализация, базы данных, 1С, файловые сервисы, видеонаблюдение, резервное копирование, терминальные подключения, аналитика или смешанная корпоративная инфраструктура.

Выбирать серверный процессор только по числу ядер или максимальной частоте — ошибка. Важно учитывать архитектуру платформы, количество сокетов, теплопакет, кэш, поддержку памяти, PCIe-линии, требования программного обеспечения, лицензирование, отказоустойчивость и перспективу роста нагрузки.

Ответственность за материал

Генеральный директор ООО «АНД-Системс»

Отвечает за стратегию ANDPRO, развитие B2B-направления, качество клиентского сервиса, поставки оборудования и экспертную базу знаний компании.

Роль в материале: авторская и управленческая экспертиза по серверным решениям, закупочным сценариям и инфраструктурным требованиям.

Главный технический специалист, системный архитектор

Проверяет техническую корректность материалов по серверным конфигурациям, процессорным платформам, совместимости, памяти, PCIe, отказоустойчивости и инфраструктурным нагрузкам.

Профессиональные сертификаты и зона ответственности указаны в профиле сотрудника.

Ответственная организация: ООО «АНД-Системс» / ANDPRO · ИНН 7733778620 · ОГРН 1117746743762 · Редакционная политика · Реквизиты

Как проверялась эта статья

Материал подготовлен как информационное руководство по выбору процессора для сервера. При обновлении проверялись: серверные сценарии нагрузки, различие между ядрами и частотой, сокетность, поддержка памяти, PCIe-линии, TDP, виртуализация, базы данных, 1С, видеонаблюдение, резервное копирование и ограничения лицензирования.

- Авторская часть проверена на соответствие B2B-сценариям закупки и инфраструктурного планирования.

- Техническая часть проверена системным архитектором ANDPRO.

- Рекомендации в статье не заменяют индивидуальный расчет серверной конфигурации.

- Перед закупкой процессор нужно проверять вместе с серверной платформой, памятью, дисками, сетевыми картами, контроллерами, ПО и лицензиями.

Коммерческий контекст материала

ANDPRO поставляет серверное оборудование, комплектующие и инфраструктурные решения. Эта статья не является товарной категорией, карточкой товара, публичной офертой или коммерческим предложением. Ее задача — объяснить, как выбирать серверный процессор под реальные задачи и какие параметры учитывать до подбора оборудования.

Если после чтения нужен подбор платформы, используйте конфигуратор серверов для предварительного расчета или перейдите в каталог серверов, где доступны товары, фильтры, наличие и цены.

1. Почему процессор важен для сервера

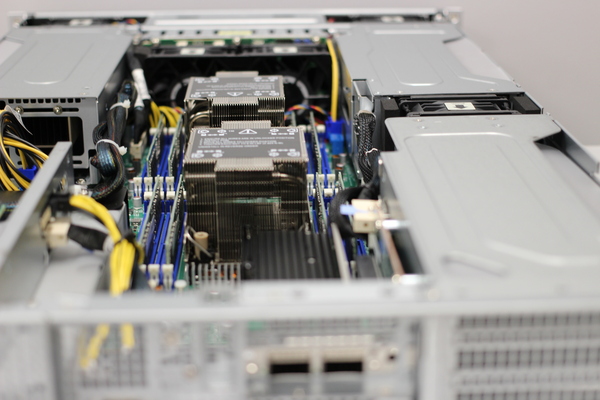

Процессор — один из ключевых компонентов сервера, но его нельзя рассматривать отдельно от всей платформы. CPU определяет вычислительные возможности системы, количество поддерживаемой памяти, число PCIe-линий, доступные серверные функции, совместимость с материнской платой и ограничения по тепловому пакету.

В реальном проекте серверный процессор должен соответствовать не абстрактной “мощности”, а конкретной роли сервера. Для виртуализации важны ядра, память и ввод-вывод. Для баз данных — частота, кэш, память и дисковая подсистема. Для 1С — баланс частоты, задержек, SQL-нагрузки и числа пользователей. Для видеонаблюдения — способность обслуживать VMS, архив, декодирование и видеоаналитику.

2. Чем серверный процессор отличается от настольного

Настольные процессоры ориентированы на персональные компьютеры и рабочие станции, где важны высокая частота, реакция интерфейса, игровые или прикладные задачи одного пользователя. Серверные процессоры рассчитаны на длительную работу, поддержку ECC-памяти, многопроцессорные конфигурации, большое число линий PCIe, расширенную диагностику и стабильность под постоянной нагрузкой.

В сервере важна не только пиковая производительность, но и предсказуемость: как CPU работает 24/7, как ведет себя при длительной нагрузке, сколько памяти поддерживает, как распределяет PCIe-устройства и какие возможности управления доступны через серверную платформу.

| Критерий | Настольный процессор | Серверный процессор |

|---|---|---|

| Основной сценарий | ПК, рабочая станция, задачи одного или нескольких пользователей. | Круглосуточная работа, сервисы, виртуализация, базы данных, корпоративная инфраструктура. |

| Память | Обычно меньший объем и ограниченная поддержка ECC. | Поддержка больших объемов памяти, ECC, RDIMM/LRDIMM в зависимости от платформы. |

| PCIe | Ограниченное число линий для видеокарты, накопителей и периферии. | Больше линий PCIe для сетевых карт, NVMe, RAID/HBA, GPU и расширителей. |

| Сокеты | Обычно однопроцессорная система. | Возможны одно- и двухсокетные платформы, иногда специализированные конфигурации. |

| Надежность | Ориентация на производительность рабочего места. | Ориентация на стабильность, диагностику, управляемость и длительную нагрузку. |

3. Ядра, потоки и частота: что важнее

Главная ошибка при выборе процессора — ориентироваться только на количество ядер. Большое число ядер полезно для виртуализации, контейнеров, многопоточных вычислений и параллельных сервисов. Но не каждая нагрузка эффективно использует десятки ядер. Некоторые приложения больше зависят от частоты, кэша, задержек памяти и производительности одного потока.

Поэтому правильный вопрос звучит не “какой процессор мощнее”, а “какой процессор лучше подходит под конкретную нагрузку”. Для одного сервера важнее высокая частота на ядро, для другого — много ядер, для третьего — объем памяти и PCIe, для четвертого — лицензирование ПО по ядрам.

Количество ядер

Важно для виртуализации, контейнеров, многопользовательских сервисов и параллельной обработки задач.

Тактовая частота

Важна для задач, чувствительных к производительности одного потока: часть СУБД, 1С, терминальные сценарии.

Потоки

SMT/Hyper-Threading помогает лучше использовать ресурсы ядра, но не заменяет реальные физические ядра.

Кэш

Больший кэш может помогать базам данных, аналитике и задачам с повторным обращением к данным.

Задержки памяти

Для некоторых нагрузок важна не только пропускная способность, но и задержка доступа к памяти.

Лицензирование

Некоторое ПО лицензируется по ядрам или сокетам, поэтому “больше ядер” не всегда экономически выгодно.

Для сервера 1С, базы данных или лицензируемого ПО иногда выгоднее выбрать процессор с меньшим числом ядер, но более высокой частотой и подходящей платформой. Для виртуализации или большого числа сервисов часто важнее суммарное число ядер, память и ввод-вывод.

4. Как выбирать процессор под разные нагрузки

Серверный процессор нужно выбирать от задачи. Универсального CPU, который одинаково хорош для всех сценариев, не существует. Один и тот же процессор может быть удачным для файлового сервера, но слабым для базы данных; избыточным для простого backup-сервера, но недостаточным для виртуализации с десятками машин.

| Сценарий | Что важно в CPU | Что проверить дополнительно |

|---|---|---|

| Виртуализация | Количество ядер, поддержка больших объемов памяти, PCIe, масштабирование. | RAM, диски, сеть, гипервизор, лицензирование, отказоустойчивость. |

| Базы данных | Частота, кэш, память, задержки, стабильность под постоянной нагрузкой. | IOPS, RAID/NVMe, объем RAM, требования СУБД, backup. |

| 1С | Баланс частоты, числа ядер, памяти и требований SQL-сервера. | Число пользователей, архитектура 1С, SQL, терминальный доступ, лицензии. |

| Файловый сервер | Умеренный CPU, стабильность, поддержка памяти и сетевых интерфейсов. | Диски, RAID, права доступа, backup, сетевые подключения. |

| Видеонаблюдение | CPU для VMS, пользователей, декодирования, аналитики и фоновых сервисов. | Битрейт камер, архив, диски, RAID, сеть, GPU при аналитике. |

| Backup-сервер | CPU для дедупликации, сжатия, шифрования и работы backup-ПО. | Сеть, репозиторий, диски, RTO/RPO, восстановление. |

| GPU/AI/HPC | PCIe-линии, поддержка GPU, память, NUMA, пропускная способность платформы. | GPU, питание, охлаждение, корпус, драйверы, совместимость. |

CPU выбирается не изолированно, а как часть платформы: серверная плата, сокеты, память, диски, RAID/HBA, сетевые карты, GPU, корпус, питание, охлаждение и программное обеспечение должны работать как единая конфигурация.

5. Сокеты, память, PCIe и серверная платформа

Выбор процессора автоматически определяет платформу: сокет, поколение серверной платы, тип памяти, количество каналов памяти, максимальный объем RAM, доступные PCIe-линии, поддержку NVMe, сетевых карт, RAID/HBA-контроллеров и GPU.

Поэтому при подборе CPU важно заранее понимать, какие компоненты будут установлены в сервер сейчас и какие могут понадобиться позже. Ошибка на уровне платформы часто ограничивает модернизацию сильнее, чем сам процессор.

Сокет

Определяет совместимость процессора с материнской платой и возможные поколения CPU.

Один или два CPU

Двухсокетная система дает больше ядер, памяти и линий ввода-вывода, но сложнее и дороже.

Каналы памяти

Влияют на пропускную способность RAM, что важно для виртуализации, баз данных и аналитики.

Объем памяти

CPU и платформа определяют максимальный объем RAM и тип поддерживаемых модулей.

PCIe-линии

Нужны для NVMe, GPU, сетевых карт, RAID/HBA, ускорителей и плат расширения.

NUMA

В многосокетных системах важно учитывать распределение памяти и устройств между процессорами.

В сервере может понадобиться несколько NVMe-накопителей, 10/25/40/100GbE-сеть, RAID/HBA, GPU или дополнительные контроллеры. Если у платформы недостаточно PCIe-линий или слотов, процессор формально мощный, но конфигурация будет ограничена.

6. TDP, охлаждение и питание

TDP процессора влияет на требования к охлаждению, блоку питания, корпусу и плотности размещения в стойке. Чем выше теплопакет, тем важнее правильно подобранное шасси, воздушный поток, вентиляторы, радиаторы, свободное пространство и условия эксплуатации серверной.

При модернизации существующего сервера нельзя просто заменить CPU на более мощный без проверки совместимости. Нужно убедиться, что BIOS/BMC поддерживает процессор, VRM рассчитан на нагрузку, система охлаждения справится с теплом, а блоки питания имеют достаточный запас.

TDP

Определяет тепловую нагрузку и требования к охлаждению сервера.

Корпус

1U, 2U, tower и GPU-шасси имеют разные ограничения по охлаждению и шуму.

Питание

CPU, GPU, диски и сетевые карты должны укладываться в мощность блоков питания с запасом.

BIOS/BMC

Процессор должен поддерживаться прошивками серверной платформы.

Температура

Нужно учитывать условия серверной, стойку, воздушные потоки и загрязнение фильтров.

Шум

Мощные серверные CPU часто требуют активного охлаждения, которое не подходит для офисного помещения.

7. Типичные ошибки при выборе процессора для сервера

Смотреть только на ядра

Много ядер не всегда лучше, особенно если ПО зависит от частоты, лицензируется по ядрам или плохо параллелится.

Игнорировать платформу

CPU может быть мощным, но ограничивать память, PCIe, сетевые карты, NVMe или будущую модернизацию.

Не учитывать лицензии

Для некоторых продуктов число ядер напрямую влияет на стоимость лицензий и итоговую экономику проекта.

Недооценивать TDP

Процессор с высоким теплопакетом требует подходящего корпуса, охлаждения и питания.

Сравнивать CPU вне задачи

Процессор нужно оценивать под конкретную нагрузку: виртуализация, 1С, БД, backup, VMS или смешанный сервер.

Забывать про рост

Если не заложить запас по памяти, PCIe и сокетам, сервер быстро перестанет соответствовать новым требованиям.

8. Чек-лист перед подбором серверного процессора

Перед выбором процессора нужно собрать исходные данные. Чем точнее вводные, тем меньше риск переплатить за избыточный CPU или выбрать платформу, которая не выдержит реальную нагрузку.

- роль сервера: виртуализация, БД, 1С, файловый сервис, backup, видеонаблюдение, GPU/AI или смешанная нагрузка;

- количество пользователей, виртуальных машин, сервисов, камер, баз данных или рабочих процессов;

- требования программного обеспечения к ядрам, частоте, памяти и лицензированию;

- нужный объем оперативной памяти сейчас и планируемый рост;

- требования к PCIe: NVMe, RAID/HBA, сетевые карты, GPU, ускорители;

- требования к отказоустойчивости: один или два CPU, резервирование, кластер, backup;

- ограничения по корпусу, стойке, шуму, теплу, питанию и серверному помещению;

- бюджет, сроки поставки, гарантия, документы и требования закупки.

10. Краткий вывод

Процессор для сервера нужно выбирать не по одному параметру, а по задаче и платформе. Количество ядер, частота, кэш, память, PCIe, TDP, сокеты, лицензирование и возможности модернизации должны рассматриваться вместе.

Для виртуализации часто важны ядра, память и ввод-вывод. Для баз данных и 1С — частота, кэш, память и дисковая подсистема. Для видеонаблюдения — взаимодействие CPU с VMS, архивом, сетью и видеоаналитикой. Для GPU/AI/HPC — PCIe, питание, охлаждение и топология платформы.

Самый надежный подход — сначала описать нагрузку, затем выбрать серверную платформу и только после этого подбирать процессор, память, диски, сетевые карты, контроллеры и корпус как единую конфигурацию.

Частые вопросы

Что важнее для сервера: частота или количество ядер?

Зависит от нагрузки. Для виртуализации и параллельных сервисов важнее число ядер. Для части баз данных, 1С и задач с высокой зависимостью от одного потока важнее частота, кэш и задержки памяти.

Можно ли использовать обычный настольный процессор в сервере?

Для некоторых простых задач это возможно, но для корпоративной инфраструктуры обычно выбирают серверную платформу с ECC-памятью, расширенной диагностикой, управлением, поддержкой больших объемов RAM и стабильной работой 24/7.

Когда нужен двухпроцессорный сервер?

Два процессора нужны, когда требуется больше ядер, памяти, PCIe-линий или масштабирование под тяжелую виртуализацию, базы данных, аналитические задачи, GPU/AI или плотную корпоративную инфраструктуру.

Почему важно учитывать лицензирование ПО?

Некоторое серверное ПО лицензируется по ядрам или сокетам. Избыточное количество ядер может увеличить стоимость владения, даже если сам процессор кажется выгодным.

Можно ли заменить процессор в существующем сервере на более мощный?

Только после проверки совместимости: сокет, поколение CPU, BIOS/BMC, питание, охлаждение, поддержка памяти, ограничения производителя и гарантийные условия.

Нужно ли выбирать процессор с запасом?

Запас нужен, но он должен быть разумным. Важно закладывать рост нагрузки, памяти, дисков, сетевых подключений и пользователей, но не переплачивать за ядра или платформу, которые не будут использоваться.