PCIe 5.0 и PCIe 4.0: в чем разница и когда нужен новый стандарт

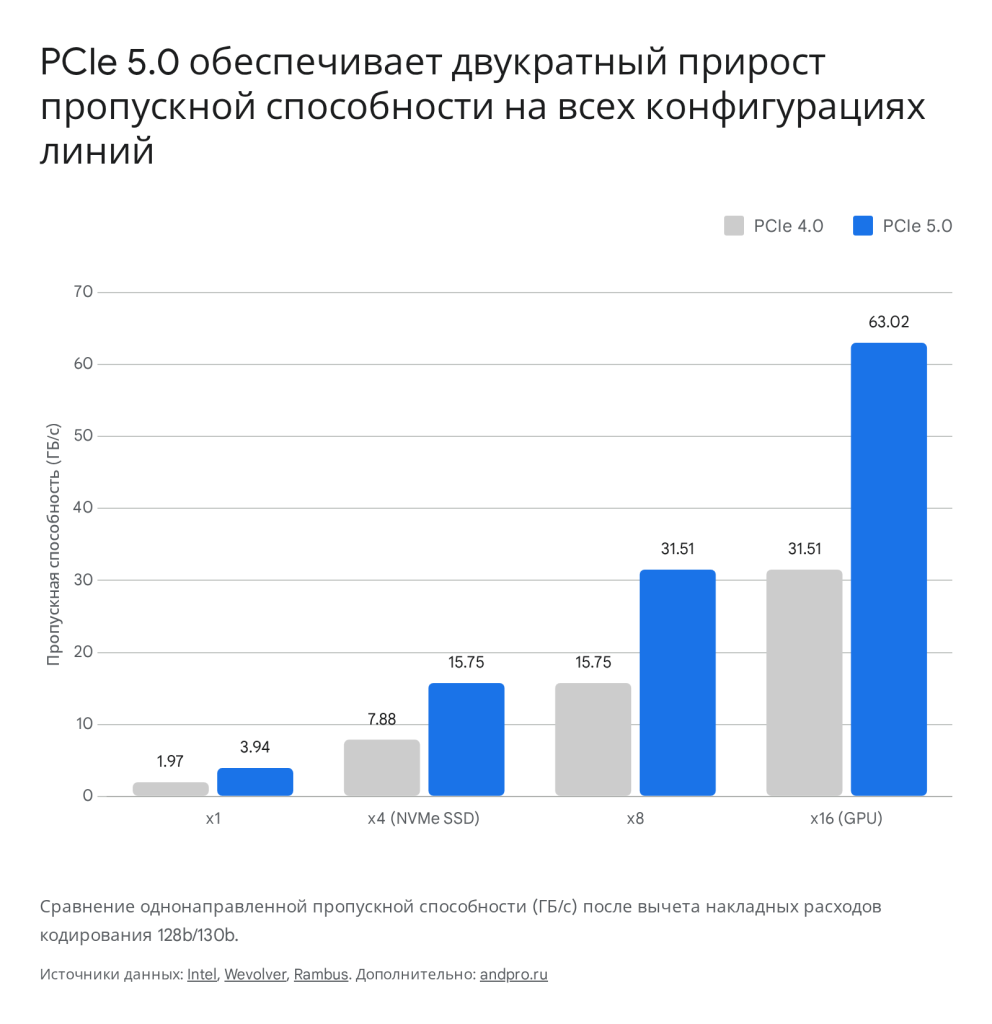

PCI Express — основная высокоскоростная шина для видеокарт, NVMe SSD, сетевых адаптеров, HBA/RAID-контроллеров, плат расширения и ускорителей вычислений. Главное отличие PCIe 5.0 от PCIe 4.0 — удвоенная скорость передачи данных на одну линию: 32 GT/s вместо 16 GT/s. На практике это означает вдвое большую пропускную способность для конфигураций x1, x4, x8 и x16.

1. Что такое PCI Express

PCI Express, или PCIe, — это последовательный интерфейс для обмена данными между процессором, чипсетом и устройствами расширения. Он используется в видеокартах, NVMe-накопителях, сетевых адаптерах, контроллерах хранения, платах захвата, ускорителях ИИ и серверных картах расширения.

В отличие от старых параллельных шин, PCIe работает по схеме «точка-точка». Соединение состоит из линий, или lanes. Одна линия обозначается как x1, четыре линии — x4, восемь — x8, шестнадцать — x16. Чем больше линий и чем новее поколение PCIe, тем выше доступная пропускная способность.

2. Главное отличие PCIe 5.0 от PCIe 4.0

PCIe 4.0 работает на скорости 16 GT/s на линию. PCIe 5.0 — на скорости 32 GT/s на линию. При одинаковой схеме кодирования 128b/130b это дает почти ровное удвоение полезной пропускной способности.

| Параметр | PCIe 4.0 | PCIe 5.0 | Практическое значение |

|---|---|---|---|

| Скорость на линию | 16 GT/s | 32 GT/s | PCIe 5.0 передает вдвое больше данных на одну линию. |

| Кодирование | 128b/130b | 128b/130b | Накладные расходы кодирования одинаковые, около 1,54%. |

| Модуляция | NRZ | NRZ | PCIe 5.0 не переходит на PAM4, чтобы не увеличивать задержки. |

| Полоса x4 | ~7,88 ГБ/с | ~15,75 ГБ/с | Критично для NVMe SSD. |

| Полоса x16 | ~31,5 ГБ/с | ~63,0 ГБ/с | Важно для ускорителей, серверов и быстрых сетевых карт. |

| Сложность платы | Высокая | Очень высокая | PCIe 5.0 требует более качественной разводки, материалов и иногда ретаймеров. |

3. Пропускная способность PCIe 4.0 и PCIe 5.0

Для пользовательских и серверных систем важнее не абстрактные GT/s, а реальная полезная полоса в гигабайтах в секунду. Ниже приведены ориентировочные однонаправленные значения до учета накладных расходов конкретных устройств и протоколов верхнего уровня.

| Конфигурация | PCIe 4.0 | PCIe 5.0 | Где встречается |

|---|---|---|---|

| x1 | ~1,97 ГБ/с | ~3,94 ГБ/с | Контроллеры USB, Wi-Fi, аудио, часть сетевых карт. |

| x4 | ~7,88 ГБ/с | ~15,75 ГБ/с | NVMe SSD, часть HBA и сетевых адаптеров. |

| x8 | ~15,75 ГБ/с | ~31,5 ГБ/с | Серверные сетевые карты, ускорители, компактные GPU-конфигурации. |

| x16 | ~31,5 ГБ/с | ~63,0 ГБ/с | Видеокарты, AI-ускорители, SmartNIC/DPU, серверные карты расширения. |

4. Обратная совместимость PCIe 5.0 и PCIe 4.0

PCIe сохраняет обратную совместимость. Устройство PCIe 5.0 можно установить в слот PCIe 4.0, а устройство PCIe 4.0 — в слот PCIe 5.0. Система согласует максимальный общий режим работы при инициализации.

| Устройство | Слот | Итоговый режим | Комментарий |

|---|---|---|---|

| PCIe 5.0 SSD | PCIe 5.0 x4 | PCIe 5.0 x4 | Максимальная скорость при наличии поддержки со стороны CPU/платы. |

| PCIe 5.0 SSD | PCIe 4.0 x4 | PCIe 4.0 x4 | Накопитель будет работать, но с ограничением по скорости интерфейса. |

| PCIe 4.0 GPU | PCIe 5.0 x16 | PCIe 4.0 x16 | Нормальный сценарий, потери совместимости нет. |

| PCIe 5.0 GPU или ускоритель | PCIe 4.0 x16 | PCIe 4.0 x16 | Работает на скорости старшего общего стандарта. |

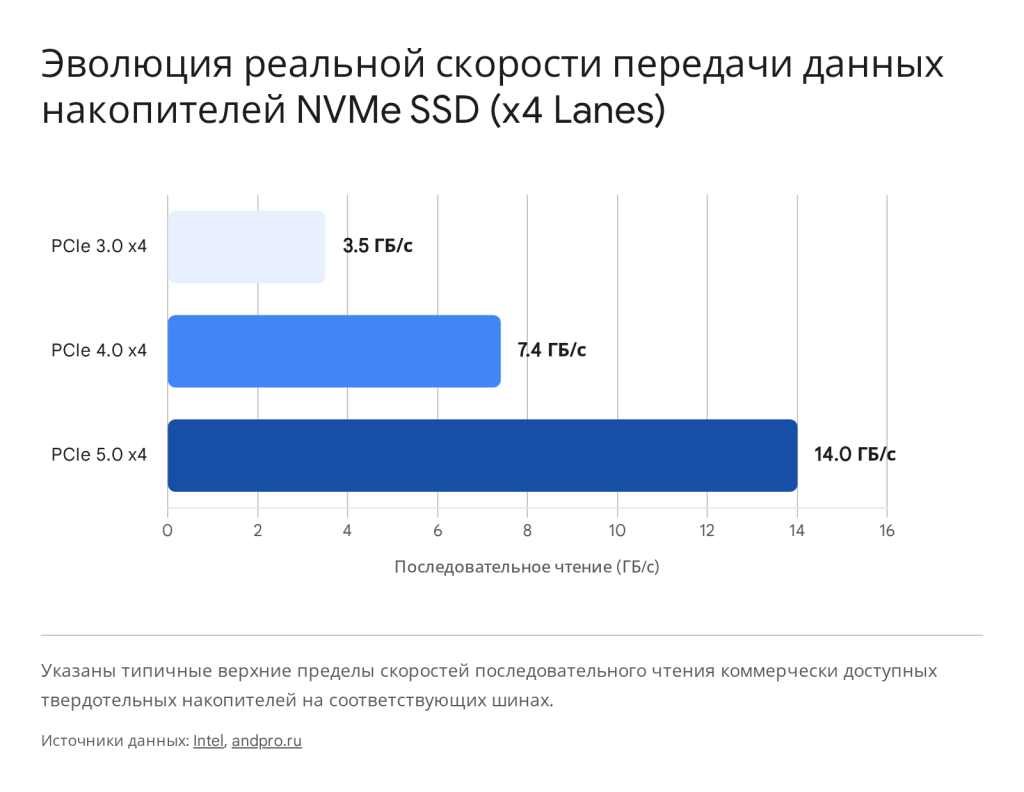

5. Влияние PCIe 5.0 на NVMe SSD

Самый заметный пользовательский эффект от PCIe 5.0 — рост скорости NVMe-накопителей. SSD PCIe 4.0 x4 обычно ограничены полосой около 7,88 ГБ/с, поэтому быстрые модели упираются в диапазон 7–7,4 ГБ/с последовательного чтения. SSD PCIe 5.0 x4 получают интерфейсный потолок около 15,75 ГБ/с и могут показывать реальные скорости чтения примерно 10–14 ГБ/с в зависимости от контроллера, NAND-памяти, прошивки и теплового режима.

Когда PCIe 5.0 SSD действительно полезен

- работа с большими медиапроектами, 6K/8K-видео, RAW и прокси-кэшами;

- локальные датасеты для ML/AI и аналитики;

- высоконагруженные рабочие станции;

- серверные All-Flash массивы и NVMe-oF;

- сценарии, где важна скорость последовательного чтения и записи;

- задачи, где несколько SSD работают параллельно и могут перегрузить чипсетный линк.

Когда PCIe 4.0 SSD достаточно

- офисная работа, браузер, документы, CRM и ERP-клиенты;

- игровой ПК без специфических задач потоковой загрузки данных;

- обычная разработка, компиляция средних проектов, локальные базы умеренного размера;

- домашний компьютер и универсальная рабочая станция;

- системный диск, где важнее надежность, ресурс и стабильность, чем пиковые ГБ/с.

6. PCIe 5.0 и видеокарты

Для большинства потребительских видеокарт переход с PCIe 4.0 x16 на PCIe 5.0 x16 не дает кратного прироста в играх. Причина проста: видеокарта использует собственную высокоскоростную видеопамять, а шина PCIe активно нагружается в основном при загрузке ресурсов, обмене с CPU, работе с DirectStorage, вычислительных задачах и нехватке VRAM.

В играх и обычных графических приложениях PCIe 4.0 x16 чаще всего остается достаточным. PCIe 5.0 становится важнее в профессиональных вычислениях, AI/ML, задачах с несколькими ускорителями, GPU Direct Storage, потоковой обработке больших массивов данных и в серверных системах.

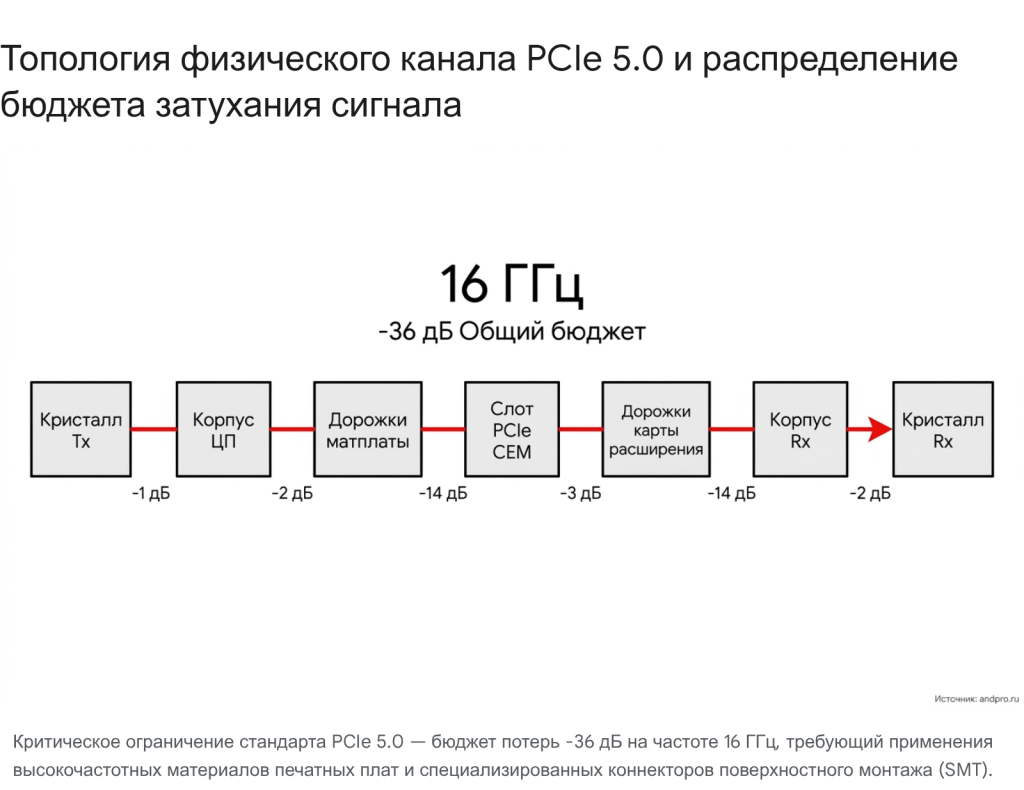

7. Почему PCIe 5.0 сложнее для материнских плат

Удвоение скорости передачи данных означает не только более высокую полосу, но и более жесткие требования к физическому уровню. На PCIe 5.0 дорожки на материнской плате работают как высокочастотные линии передачи. Важны длина трасс, качество текстолита, согласование импеданса, переходные отверстия, разъемы, качество питания и уровень помех.

Что усложняется в PCIe 5.0

- Материал платы. Для длинных линий нужны диэлектрики с меньшими потерями.

- Разводка. Требуются строгие допуски по длинам дифференциальных пар и импедансу.

- Переходные отверстия. На высоких частотах лишние участки via могут ухудшать сигнал.

- Ретаймеры. В серверных платформах и сложных топологиях нужны микросхемы восстановления сигнала.

- Тепловой режим. Быстрые SSD и ретаймеры выделяют дополнительное тепло.

8. Ретаймеры и редрайверы: зачем они нужны

На коротких трассах от процессора до первого PCIe-слота или M.2-разъема сигнал может передаваться без активного восстановления. Но в серверных системах, бэкплейнах, riser-картах, GPU-шасси и плотных NVMe-полках длина трассы и количество разъемов растут. В таких случаях пассивной разводки уже недостаточно.

Редрайвер усиливает аналоговый сигнал, но вместе с ним может усиливать шум и джиттер. Ретаймер работает сложнее: принимает сигнал, восстанавливает тактирование, очищает его от части искажений и заново формирует сигнал для следующего участка линии. Поэтому в PCIe 5.0-серверах ретаймеры часто становятся обязательной частью архитектуры.

| Компонент | Что делает | Плюсы | Минусы |

|---|---|---|---|

| Редрайвер | Усиливает и корректирует аналоговый сигнал. | Проще, дешевле, меньше задержка. | Не восстанавливает сигнал полностью, может усиливать шум. |

| Ретаймер | Принимает, восстанавливает тактирование и заново передает сигнал. | Лучше для длинных трасс, бэкплейнов и Gen5-серверов. | Дороже, горячее, сложнее в проектировании. |

9. PCIe 5.0 в серверах, СХД и сетевых адаптерах

В серверном сегменте PCIe 5.0 имеет гораздо большее значение, чем в обычных ПК. Причина — высокая плотность устройств и большие потоки данных. Один сервер может содержать несколько NVMe SSD, HBA, GPU-ускорители, SmartNIC, DPU и сетевые карты 100/200/400GbE.

Для сетевых адаптеров класса 200GbE и 400GbE PCIe 4.0 может стать ограничением. Например, 400GbE создает поток порядка 50 ГБ/с в одном направлении до учета накладных расходов. Для такой нагрузки PCIe 5.0 x16 дает необходимый запас, тогда как PCIe 4.0 x16 находится ближе к пределу.

Где PCIe 5.0 особенно важен

- серверы виртуализации с большим числом NVMe-накопителей;

- All-Flash СХД и NVMe-oF;

- GPU-серверы для AI/ML и инференса;

- системы с DPU, SmartNIC и сетями 200/400GbE;

- платформы с PCIe-switch и несколькими ускорителями;

- высокоплотные серверы с бэкплейнами и riser-картами.

10. Практический выбор: PCIe 4.0 или PCIe 5.0

| Сценарий | Достаточно PCIe 4.0? | Есть смысл в PCIe 5.0? | Комментарий |

|---|---|---|---|

| Офисный ПК | Да | Обычно нет | Пиковая скорость PCIe редко влияет на пользовательский опыт. |

| Игровой ПК | Да | Скорее как запас | Для GPU важнее производительность видеокарты и объем VRAM. |

| Рабочая станция с быстрым SSD | Часто да | Да, при больших проектах | PCIe 5.0 SSD полезен для видео, данных, кэшей и тяжелых проектов. |

| Домашний NAS / SOHO | Да | Редко | Чаще ограничением будет сеть, диски или CPU, а не PCIe 4.0. |

| Сервер виртуализации | Зависит от нагрузки | Да | PCIe 5.0 полезен при нескольких NVMe, HBA, 25/100GbE и GPU. |

| AI/ML-сервер | Иногда недостаточно | Да | Высокая полоса нужна для обмена CPU-GPU, GPU-GPU, SSD-GPU и сети. |

| 400GbE-сеть | Нет или на пределе | Да | PCIe 5.0 x16 дает достаточную полосу для высокоскоростных сетевых карт. |

11. Чек-лист перед покупкой платы или устройства PCIe 5.0

12. Типичные ошибки

- покупать PCIe 5.0 SSD без радиатора и нормального обдува;

- считать, что любой слот x16 работает в режиме x16;

- не учитывать, что M.2-разъемы могут делить линии с PCIe-слотами или SATA;

- использовать PCIe 4.0 riser-кабель для устройства PCIe 5.0;

- выбирать дорогую плату Gen5 для задач, где достаточно PCIe 4.0;

- не проверять совместимость HBA, DPU, GPU и NVMe в серверной платформе;

- игнорировать нагрев ретаймеров, SSD и плотных PCIe-устройств.

13. Что выбрать в 2026 году

Для обычного ПК, офисной системы и большинства игровых сборок PCIe 4.0 остается рациональным и достаточным стандартом. Он обеспечивает высокую скорость для видеокарт и NVMe SSD, а также позволяет собрать сбалансированную систему без переплаты за Gen5-инфраструктуру.

PCIe 5.0 стоит выбирать, если система строится с расчетом на быстрые NVMe SSD, профессиональные рабочие нагрузки, серверную виртуализацию, GPU-ускорители, AI/ML, высокоскоростные сетевые карты, плотные подсистемы хранения или длительный жизненный цикл платформы.

Нужна проверка PCIe-топологии перед покупкой?

Специалисты ANDPRO помогут проверить совместимость материнской платы, процессора, NVMe SSD, видеокарт, HBA/RAID-контроллеров, сетевых адаптеров и riser-карт под вашу задачу.

Email: info@andpro.ru

Телефон: +7 (495) 545-48-70

14. Часто задаваемые вопросы

PCIe 5.0 быстрее PCIe 4.0 в два раза?

Да, на уровне интерфейса PCIe 5.0 удваивает скорость передачи на одну линию: 32 GT/s вместо 16 GT/s. Например, PCIe 5.0 x4 дает примерно такую же полосу, как PCIe 4.0 x8.

Будет ли PCIe 5.0 SSD работать в слоте PCIe 4.0?

Да, будет. Но он переключится в режим PCIe 4.0 и будет ограничен пропускной способностью этого стандарта. Для максимальной скорости нужен слот PCIe 5.0 x4 и поддержка со стороны процессора и материнской платы.

Нужен ли PCIe 5.0 для видеокарты?

Для большинства игровых видеокарт PCIe 4.0 x16 достаточно. PCIe 5.0 важнее для профессиональных ускорителей, AI/ML, многопроцессорных серверных конфигураций и задач с интенсивным обменом данных.

Почему PCIe 5.0 SSD сильнее греются?

Быстрые PCIe 5.0 SSD используют более сложные контроллеры и работают с высокой скоростью обмена. Это увеличивает энергопотребление и тепловыделение. Поэтому для них особенно важны радиатор, термопрокладка и обдув.

Можно ли использовать PCIe 4.0 riser для PCIe 5.0 видеокарты?

Физически иногда можно, но стабильность режима PCIe 5.0 не гарантируется. Система может перейти на PCIe 4.0 или работать нестабильно. Для Gen5 лучше использовать сертифицированный riser, рассчитанный на PCIe 5.0.

Что важнее: PCIe 5.0 или больше линий PCIe?

Зависит от задачи. Для одного быстрого SSD важен Gen5 x4. Для сервера с несколькими GPU, HBA, сетевыми картами и NVMe часто важнее общее количество линий, корректная бифуркация и топология подключения.

15. Итог

PCIe 5.0 — это не просто «новее и быстрее», а стандарт для задач, где пропускная способность ввода-вывода становится ограничением. Он удваивает полосу PCIe 4.0, но требует более качественной материнской платы, более строгой трассировки, лучшего охлаждения SSD и внимательной проверки совместимости.

Для массовых ПК PCIe 4.0 остается практичным выбором. Для серверов, быстрых NVMe, AI/ML, высокоскоростных сетей и долгосрочных профессиональных платформ PCIe 5.0 уже имеет реальную инженерную ценность.

Автор статьи: Сергей Коваль. Технический аудит и экспертная оценка: Михаил Биркос.