Виды VRM материнской платы: какие бывают топологии и что выбрать

VRM материнской платы — это силовая подсистема, которая преобразует напряжение блока питания в стабильное питание для процессора, встроенной графики, контроллера памяти и других узлов. От качества VRM зависит не только разгон, но и базовая стабильность системы под длительной нагрузкой, температура силовой зоны, шум вентиляторов, срок службы компонентов и запас для будущего апгрейда.

1. Что такое VRM и почему он важен

VRM — Voltage Regulator Module, модуль регулирования напряжения. На материнской плате он принимает входное напряжение от блока питания, обычно 12 В по линиям EPS/ATX12V, и преобразует его в низкое напряжение, которое требуется процессору. Для современных CPU это часто диапазон около 0.7–1.4 В, но при этом токи могут достигать сотен ампер.

Именно поэтому VRM работает не как простой стабилизатор, а как многофазный синхронный понижающий импульсный преобразователь. Он должен быстро реагировать на изменения нагрузки: процессор может за микросекунды перейти от простоя к полной загрузке, а затем так же резко сбросить потребление. Если VRM не успевает отработать такие переходы, возникают просадки напряжения, перегрев, сбои вычислений, перезагрузки или троттлинг.

2. Из чего состоит VRM материнской платы

Типовая фаза VRM включает ШИМ-контроллер, драйвер, силовые MOSFET или интегрированную сборку DrMOS/SPS, дроссель и массив фильтрующих конденсаторов. В многофазной схеме несколько таких фаз работают параллельно, но включаются с фазовым сдвигом. Это снижает пульсации и распределяет тепловую нагрузку.

| Компонент | Назначение | На что смотреть при выборе платы |

|---|---|---|

| ШИМ-контроллер | Управляет фазами, задает частоту переключения, напряжение и реакцию на нагрузку. | Количество реальных каналов, поддержка телеметрии, качество алгоритмов LLC и защиты. |

| MOSFET / DrMOS / SPS | Коммутирует ток, физически преобразуя 12 В в низкое напряжение CPU. | Токовый рейтинг, КПД, температурная телеметрия, тип корпуса и охлаждение. |

| Дроссель | Запасает энергию в магнитном поле и сглаживает ток. | Ток насыщения, DCR, качество сердечника, нагрев под длительной нагрузкой. |

| Конденсаторы | Фильтруют пульсации и помогают выдерживать резкие скачки нагрузки. | Низкие ESR/ESL, сочетание полимерных конденсаторов и MLCC у сокета. |

| Радиаторы VRM | Отводят тепло от силовых каскадов и дросселей. | Масса, площадь ребер, термопрокладки, наличие реального контакта с DrMOS/SPS. |

3. Почему количество фаз не равно качеству VRM

Маркетинговые обозначения вроде «16+2+1 фаз» или «20-фазное питание» не всегда означают, что плата имеет 20 полностью независимых каналов управления. Производители могут использовать прямые фазы, удвоители, параллельные силовые каскады или комбинированные схемы. Поэтому две платы с одинаковым числом «фаз» на коробке могут радикально отличаться по переходной характеристике, температуре и стабильности.

Корректная оценка VRM должна учитывать не только количество фаз, но и токовый запас силовых каскадов. Например, 10 фаз на качественных SPS по 90 А могут быть лучше, чем 16 условных фаз на более слабых дискретных MOSFET с плохим охлаждением.

4. Основные виды топологий VRM

В современных материнских платах чаще всего встречаются три подхода: прямые фазы, фазы с удвоителями и параллельная архитектура Teamed / Twin Power Stages. У каждой схемы есть собственный инженерный смысл.

4.1. Прямая топология: True Phase / Direct VRM

В прямой топологии каждый канал ШИМ-контроллера управляет одним силовым каскадом. Это наиболее чистая архитектура: управляющий сигнал проходит без дополнительных логических микросхем, задержка минимальна, а контроллер точно управляет каждой фазой.

- Плюсы: быстрый отклик на скачки нагрузки, точное управление фазами, хорошая стабильность.

- Минусы: дорогие многофазные контроллеры, сложная разводка, высокая себестоимость платы.

- Где уместно: флагманские платы, рабочие станции, HEDT, платы для длительной высокой нагрузки.

4.2. Топология с удвоителями: Phase Doubler

Удвоитель фаз принимает один управляющий сигнал от ШИМ-контроллера и поочередно распределяет его на два силовых каскада. Такая схема позволяет увеличить физическое количество силовых элементов и распределить тепло по большей площади, не используя дорогой контроллер с большим числом каналов.

- Плюсы: хорошее распределение тепла, снижение пульсаций, экономичность.

- Минусы: дополнительная задержка сигнала, не самый быстрый отклик на резкие скачки тока.

- Где уместно: массовые платы среднего и верхнего сегмента, игровые сборки без экстремального разгона.

4.3. Параллельная топология: Teamed / Twin Power Stages

В параллельной схеме один канал ШИМ-контроллера одновременно управляет двумя силовыми каскадами. Микросхемы-удвоители не используются, поэтому задержка меньше, чем в схеме с doubler. При этом ток делится между двумя DrMOS/SPS, а тепловая нагрузка распределяется по большей площади.

- Плюсы: быстрый отклик, высокий токовый запас, хорошее распределение тепла.

- Минусы: пульсации могут быть выше, чем у схемы с идеальным фазовым чередованием; требуется качественная фильтрация.

- Где уместно: современные платы среднего и верхнего уровня, мощные игровые ПК, рабочие станции.

| Критерий | True / Direct | Phase Doubler | Teamed / Twin |

|---|---|---|---|

| Схема управления | 1 PWM-канал → 1 силовой каскад. | 1 PWM-канал → удвоитель → 2 силовых каскада. | 1 PWM-канал → 2 силовых каскада параллельно. |

| Задержка управляющего сигнала | Минимальная. | Выше из-за логики удвоителя. | Минимальная, так как удвоителя нет. |

| Переходная характеристика | Очень хорошая. | Средняя или хорошая, зависит от реализации. | Очень хорошая при качественных SPS и фильтрации. |

| Подавление пульсаций | Хорошее. | Очень хорошее за счет фазового чередования. | Зависит от конденсаторов и частоты переключения. |

| Тепловое распределение | Зависит от количества реальных фаз. | Хорошее: больше физических каскадов. | Хорошее: ток делится между каскадами. |

| Себестоимость | Высокая. | Средняя. | Средняя или высокая, зависит от класса SPS. |

| Практический вывод | Лучший вариант при грамотной реализации, но дорогой. | Нормально для массовых плат, если силовая часть не слабая. | Один из самых практичных вариантов для современных мощных CPU. |

5. DrMOS, SPS и дискретные MOSFET: в чем разница

Старые и бюджетные платы могут использовать дискретные MOSFET: отдельный драйвер, верхний MOSFET и нижний MOSFET. Такая схема работает, но имеет больше паразитных индуктивностей, хуже масштабируется по частоте и сильнее зависит от качества разводки платы.

DrMOS объединяет драйвер и силовые транзисторы в одном корпусе. Это снижает потери, улучшает скорость переключения и упрощает охлаждение. Smart Power Stage — более продвинутый вариант, где дополнительно интегрированы датчики тока и температуры. SPS передает контроллеру точные данные по каждой фазе, что помогает балансировать нагрузку и защищать VRM от перегрева.

| Тип силовой части | Описание | Плюсы | Минусы |

|---|---|---|---|

| Дискретные MOSFET | Драйвер и транзисторы распаяны отдельными компонентами. | Низкая стоимость, простота для бюджетных плат. | Выше потери, больше нагрев, хуже телеметрия. |

| DrMOS | Драйвер, High-side и Low-side MOSFET в одном корпусе. | Выше КПД, меньше паразитные эффекты, компактность. | Качество сильно зависит от конкретной модели и охлаждения. |

| Smart Power Stage | Интегрированный силовой каскад с датчиками тока и температуры. | Точная телеметрия, лучшая защита, высокий токовый запас. | Выше стоимость, используется не во всех сегментах. |

6. Vdroop, LLC и переходные процессы

Когда процессор резко увеличивает потребление, напряжение на ядре проседает. Это называется Vdroop. Полностью устранять Vdroop не всегда правильно: контролируемая просадка нужна, чтобы избежать опасных выбросов напряжения при резком снятии нагрузки. Поэтому производители процессоров задают нагрузочную линию — зависимость напряжения от тока.

Load-Line Calibration, или LLC, меняет поведение этой нагрузочной линии. Агрессивный LLC может удерживать напряжение ближе к заданному значению под нагрузкой, но повышает риск пиковых выбросов. Умеренный LLC безопаснее для повседневной эксплуатации, особенно в рабочих станциях и системах, которые работают под долгой нагрузкой.

7. Термодинамика VRM: почему радиаторы важны не меньше фаз

Все потери в VRM превращаются в тепло. Основные источники потерь — сопротивление открытого канала транзисторов, коммутационные потери при переключении, нагрев дросселей и потери в печатной плате. Чем выше ток CPU и чем дольше нагрузка, тем важнее становятся радиаторы, термопрокладки и airflow корпуса.

В кратковременном бенчмарке слабый VRM может выглядеть приемлемо. Но при длительном рендеринге, компиляции, работе с виртуальными машинами, инженерным ПО или базами данных силовая зона выходит на тепловое плато. Если радиаторы малы или плохо контактируют с DrMOS/SPS, плата снижает частоты процессора или перегревает силовую часть.

8. Как выбрать VRM под задачу

Правильный выбор зависит от процессора и сценария. Офисному ПК не нужна флагманская плата с массивной силовой зоной. Но для Core i9, Ryzen 9, рабочих станций, рендеринга, виртуализации и длительных AVX-нагрузок экономия на VRM быстро превращается в троттлинг, шум и снижение ресурса.

| Сценарий | Минимально разумный VRM | На что обратить внимание |

|---|---|---|

| Офисный ПК / базовая сборка | Базовый VRM с радиатором на зоне питания. | Стабильность, наличие радиатора, поддержка нужного CPU без перегрева. |

| Игровой ПК среднего уровня | DrMOS или качественные MOSFET, умеренное количество фаз. | Температуры VRM в играх, поддержка XMP/EXPO, нормальный airflow. |

| Мощный игровой ПК | DrMOS/SPS, хорошее охлаждение, практичная Teamed или Direct-топология. | Запас под boost CPU, стабильность памяти, охлаждение зоны VRM при СЖО. |

| Рабочая станция | SPS с телеметрией, массивные радиаторы, запас по току. | Поведение под длительной нагрузкой, отсутствие VRM throttling, надежность. |

| Сервер / 24/7 / виртуализация | Силовая зона с большим запасом, телеметрия, предсказуемые настройки питания. | Стабильность, ECC-память, BMC/IPMI при необходимости, документированная совместимость. |

| Экстремальный разгон | Премиальная Direct или Teamed-архитектура, SPS высокого тока, усиленное охлаждение. | LLC, ручные напряжения, температурный запас, качество BIOS и защиты. |

9. Практический чек-лист оценки материнской платы

Перед покупкой материнской платы имеет смысл проверить не только чипсет, количество M.2 и внешний вид, но и силовую часть. Особенно если планируется установка процессора верхнего сегмента.

10. Типовые ошибки при оценке VRM

- Считать фазы по надписям на коробке. Маркетинговое число не всегда отражает реальные независимые каналы.

- Игнорировать радиаторы. Даже качественные SPS нуждаются в нормальном теплоотводе.

- Ставить мощный CPU на плату начального уровня. Система может стартовать, но терять частоты при длительной нагрузке.

- Использовать СЖО без обдува зоны VRM. Башенный кулер частично обдувает плату, а СЖО часто оставляет VRM без потока воздуха.

- Ставить максимальный LLC без проверки. Это может создать опасные выбросы напряжения.

- Путать кратковременную стабильность с надежностью 24/7. Для рабочих задач важна длительная проверка температур.

11. Перспектива: 48 В и новые архитектуры питания

В серверных, телекоммуникационных и высокоплотных вычислительных системах развивается переход к распределению питания по более высоким напряжениям, включая 48 В. Идея проста: при повышении напряжения ток в силовых шинах снижается, а тепловые потери в проводниках уменьшаются квадратично. Это особенно важно для AI-серверов, GPU-узлов и стоечных систем с высокой плотностью мощности.

Для обычных десктопных материнских плат классическая 12-вольтовая архитектура пока остается нормой. Но тренд на рост токов и тепловых пакетов уже влияет на дизайн: силовые каскады становятся умнее, телеметрия точнее, радиаторы массивнее, а требования к печатной плате выше.

12. Часто задаваемые вопросы

Чем больше фаз VRM, тем лучше?

Не всегда. Большее количество фаз помогает распределить тепло и снизить пульсации, но качество зависит от реальной топологии, типа силовых каскадов, радиаторов, ШИМ-контроллера и настроек BIOS. Хорошая 10- или 12-фазная схема на сильных SPS может быть лучше слабой «16-фазной» реализации.

Что лучше: Direct, Doubler или Teamed?

Для максимальной точности управления хороша Direct-топология. Doubler полезен для распределения тепла и подавления пульсаций, но вносит задержку. Teamed-топология часто является удачным компромиссом: быстрый отклик, высокий токовый запас и разумная себестоимость при условии качественной фильтрации.

Нужен ли мощный VRM, если я не разгоняю процессор?

Да, если используется процессор верхнего сегмента или длительные нагрузки: рендеринг, компиляция, виртуализация, расчеты, обработка видео, базы данных. Современный boost сам повышает частоты и энергопотребление, поэтому VRM влияет на стабильность даже без ручного разгона.

Почему VRM греется сильнее при СЖО?

Башенный кулер процессора обычно создает поток воздуха вокруг сокета и частично охлаждает радиаторы VRM. Система жидкостного охлаждения переносит радиатор на корпус, поэтому зона VRM может остаться без локального обдува. В таком случае важны корпусные вентиляторы.

Что такое DrMOS и SPS?

DrMOS — интегрированный силовой каскад, объединяющий драйвер и MOSFET в одном корпусе. SPS, или Smart Power Stage, дополнительно содержит датчики тока и температуры. SPS дает более точную телеметрию и лучше подходит для мощных процессоров.

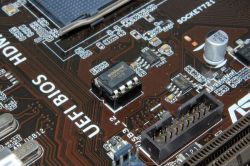

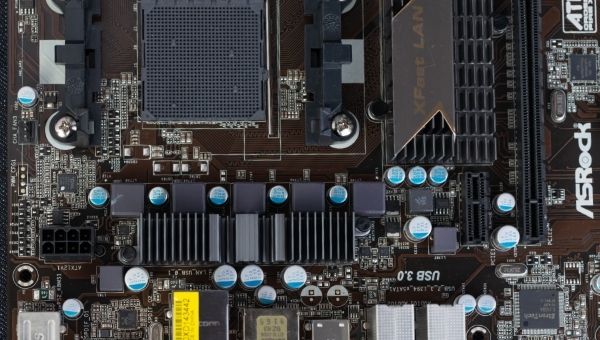

Можно ли понять качество VRM по фотографии платы?

Частично. По фотографии можно оценить радиаторы, количество дросселей и общий класс платы, но нельзя точно определить качество силовых каскадов, реальную топологию и поведение под нагрузкой. Для точной оценки нужны спецификации, разбор компонентной базы и тесты температур.

13. Итог

VRM материнской платы — это не декоративная характеристика, а один из ключевых узлов стабильности всей системы. При выборе платы важно смотреть не на одно число фаз, а на совокупность факторов: топологию, силовые каскады, радиаторы, телеметрию, BIOS, настройки LLC и сценарий эксплуатации.

Для офисных и базовых систем достаточно простой, но охлаждаемой силовой зоны. Для игровых ПК среднего уровня разумен качественный DrMOS. Для мощных процессоров, рабочих станций и длительной нагрузки предпочтительны платы с хорошими SPS, массивными радиаторами и продуманной топологией Direct или Teamed. Экономия на VRM оправдана только тогда, когда процессор и нагрузка действительно не требуют большого токового и теплового запаса.

Автор статьи: Сергей Коваль. Технический аудит и экспертная оценка: Михаил Биркос.