Серверные материнские платы: функции, типы и форм-факторы

Серверная материнская плата — основа вычислительного узла, от которой зависят совместимость процессоров, объем памяти, количество PCIe-линий, поддержка накопителей, удаленное управление, отказоустойчивость и дальнейшая модернизация сервера.

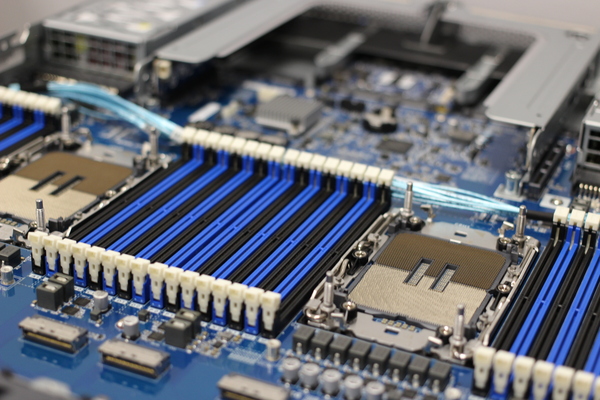

В отличие от обычных desktop-плат, серверные платы проектируются для длительной работы под нагрузкой, установки в стойки, поддержки ECC-памяти, удаленного администрирования через BMC/IPMI, подключения большого количества накопителей, сетевых адаптеров, RAID/HBA-контроллеров и других плат расширения.

Кратко

- Серверная плата определяет архитектуру сервера: процессоры, память, PCIe, сеть, накопители и управление.

- Главные отличия от desktop-плат: ECC-память, BMC/IPMI, больше PCIe-линий, поддержка серверных CPU и работа 24/7.

- Критичные параметры: сокет, чипсет, форм-фактор, совместимость памяти, число слотов PCIe, питание, охлаждение и HCL/QVL.

- Типовые сценарии: виртуализация, файловые серверы, СХД, базы данных, GPU-вычисления, резервное копирование и инфраструктурные сервисы.

- Главный риск выбора: физическая совместимость не гарантирует электрическую, тепловую и firmware-совместимость.

Автор и техническая проверка

- Автор: Сергей Коваль, ANDPRO, koval@andpro.ru

- Технический аудит: Михаил Биркос, системный архитектор ANDPRO, birkos@andpro.ru

- Что проверялось: корректность терминологии, совместимость серверных компонентов, форм-факторы, ограничения PCIe, память ECC, удаленное управление и практические сценарии выбора.

1. Что такое серверная материнская плата

Серверная материнская плата — это печатная плата, на которой размещаются процессорные сокеты, слоты оперативной памяти, разъемы питания, интерфейсы накопителей, слоты расширения, контроллеры управления и другие элементы, необходимые для работы сервера.

Ее задача — не просто «соединить компоненты», а обеспечить стабильную работу оборудования в заданной конфигурации: под нагрузкой, в нужном тепловом режиме, с поддержкой удаленного мониторинга, резервирования и обслуживания.

2. Чем серверная плата отличается от обычной материнской платы

| Параметр | Desktop-плата | Серверная плата |

|---|---|---|

| Назначение | ПК, рабочая станция, игровая или офисная система. | Сервер, СХД, узел виртуализации, вычислительный или инфраструктурный узел. |

| Процессоры | Обычно один CPU потребительского или workstation-сегмента. | Один или несколько серверных CPU, рассчитанных на длительную нагрузку. |

| Память | Обычно UDIMM, часто без ECC. | ECC UDIMM, RDIMM, LRDIMM или другие серверные типы памяти в зависимости от платформы. |

| Удаленное управление | Чаще отсутствует. | BMC/IPMI/Redfish для удаленного включения, мониторинга, KVM и просмотра логов. |

| PCIe-линии | Ограниченное количество линий и слотов. | Больше линий для сетевых карт, HBA/RAID, NVMe, GPU и специализированных адаптеров. |

| Режим работы | Периодическая пользовательская нагрузка. | Круглосуточная работа 24/7, часто в стойке и под длительной нагрузкой. |

3. Основные функции серверной материнской платы

Функции серверной платы зависят от платформы, но ключевые задачи обычно одинаковы: поддержать нужный CPU, память, платы расширения, накопители, сеть, удаленное управление и мониторинг состояния оборудования.

- Поддержка серверных процессоров. Сокет и чипсет определяют поколение CPU, количество ядер, частоты, TDP и доступные линии PCIe.

- Работа с ECC-памятью. ECC снижает риск некорректных вычислений из-за одиночных ошибок памяти.

- Поддержка плат расширения. HBA, RAID, сетевые адаптеры, GPU, ускорители, платы видеозахвата и другие PCIe-устройства.

- Интерфейсы хранения. SATA, SAS через HBA/RAID, NVMe, SlimSAS, OCuLink, U.2/U.3 — в зависимости от модели платы и шасси.

- Удаленное управление. BMC/IPMI позволяет администрировать сервер без физического доступа к нему.

- Мониторинг. Контроль температур, вентиляторов, напряжений, ошибок памяти, питания и журналов событий.

4. Сокеты и процессорные платформы

Сокет — один из первых параметров при выборе серверной платы. Он определяет, какие процессоры можно установить, сколько каналов памяти будет доступно, какой TDP поддерживается и сколько PCIe-линий может использовать система.

| Платформа | Типичный сценарий | На что обратить внимание |

|---|---|---|

| Однопроцессорная серверная плата | Файловый сервер, небольшой узел виртуализации, резервное копирование, инфраструктурные сервисы. | Достаточность PCIe-линий, объем памяти, поддержка нужных накопителей и сетевых карт. |

| Двухпроцессорная серверная плата | Высокая плотность ядер, виртуализация, базы данных, вычислительные задачи. | NUMA-архитектура, баланс памяти по CPU, тепловой пакет, питание и совместимость шасси. |

| Плата для GPU-сервера | AI/ML, рендеринг, VDI, вычисления на ускорителях. | Количество PCIe x16, расстояние между слотами, питание GPU, охлаждение и поддержка райзеров. |

| Плата для СХД | ZFS, Ceph, NAS, backup-хранилище, дисковые полки. | HBA-совместимость, PCIe-линии, поддержка ECC, сеть 10/25/100GbE, IPMI и стабильность под I/O-нагрузкой. |

Важно о совместимости CPU

Даже если процессор физически подходит к сокету, это не гарантирует работу в конкретной плате. Нужно проверять BIOS/UEFI-версию, список поддерживаемых CPU, TDP, stepping, требования к питанию и совместимость с выбранной памятью.

5. ECC-память: зачем она нужна серверу

ECC-память умеет обнаруживать и исправлять отдельные ошибки в ячейках памяти. Для серверов это особенно важно, потому что ошибка в памяти может привести к повреждению данных, сбою виртуальной машины, падению базы данных или некорректной работе файловой системы.

Тип памяти зависит от платформы. В серверных системах встречаются ECC UDIMM, RDIMM, LRDIMM и другие варианты. Нельзя выбирать память только по частоте и объему: необходимо проверять тип модуля, ранги, поддерживаемые частоты, количество модулей на канал и список совместимости платы.

6. Форм-факторы серверных материнских плат

Форм-фактор определяет физический размер платы, расположение монтажных отверстий, совместимость с корпусом, направление воздушного потока, доступность слотов расширения и удобство обслуживания.

| Форм-фактор | Где используется | Особенности выбора |

|---|---|---|

| ATX | Башенные серверы, небольшие серверы, рабочие станции. | Удобен для универсальных конфигураций, но не всегда оптимален для плотной стоечной установки. |

| Micro-ATX | Компактные серверы, NAS, небольшие инфраструктурные узлы. | Меньше слотов расширения, но проще подобрать компактный корпус. |

| SSI-CEB | Серверные и workstation-платформы повышенной функциональности. | Нужно проверять совместимость корпуса и расположение стоек крепления. |

| SSI-EEB | Двухпроцессорные серверы, мощные рабочие станции, GPU-системы. | Требует корпуса с поддержкой большого размера платы, правильного питания и охлаждения. |

| Проприетарные форм-факторы | Платформы конкретных производителей, blade-серверы, плотные 1U/2U-решения. | Высокая интеграция, но ограниченная заменяемость и зависимость от конкретного шасси. |

7. PCIe, сетевые карты, HBA и GPU

Один из ключевых параметров серверной платы — число и распределение PCIe-линий. Именно от них зависит, можно ли одновременно установить быстрые сетевые карты, HBA/RAID-контроллеры, NVMe-адаптеры, GPU или другие платы расширения без падения скорости.

Сервер виртуализации

Важны слоты для сетевых карт, достаточный объем ECC-памяти, поддержка нескольких NVMe-накопителей и удаленное управление.

СХД или NAS

Важны HBA-контроллеры, стабильная работа с дисками, ECC-память, IPMI, быстрые сетевые интерфейсы и совместимость с файловой системой.

GPU-сервер

Важны полноскоростные PCIe x16, расстояние между слотами, питание, airflow, поддержка райзеров и совместимость ускорителей.

8. BMC, IPMI и удаленное управление

BMC — отдельный контроллер управления на серверной плате. Он работает независимо от основной операционной системы и позволяет администратору подключаться к серверу удаленно, включать и выключать питание, смотреть датчики, проверять логи и работать через удаленную консоль.

Для серверов, которые размещены в стойке, офисной серверной, ЦОД или удаленной площадке, наличие BMC/IPMI значительно упрощает обслуживание. Без него многие операции требуют физического доступа к оборудованию.

9. Как выбрать серверную материнскую плату под задачу

Чек-лист выбора

- Определите задачу: виртуализация, СХД, база данных, GPU, backup, инфраструктурный сервер или файловое хранилище.

- Выберите платформу CPU: один или два процессора, нужное число ядер, TDP, PCIe-линии и поддержка памяти.

- Проверьте память: ECC, тип модулей, максимальный объем, число каналов, QVL и правила заполнения слотов.

- Проверьте PCIe: количество слотов, физический размер, электрический режим x16/x8/x4, поддержка райзеров.

- Проверьте накопители: SATA, SAS через HBA, NVMe, U.2/U.3, SlimSAS, OCuLink и совместимость с корпусом.

- Проверьте сеть: встроенные интерфейсы и возможность установки 10/25/40/100GbE-адаптеров.

- Проверьте управление: BMC/IPMI, удаленная консоль, мониторинг датчиков и журналов.

- Проверьте корпус: форм-фактор, монтажные отверстия, airflow, высота радиаторов, доступность портов и кабелей.

- Проверьте питание: разъемы EPS, требования CPU, GPU, дисков и резерв по блоку питания.

- Сверьте HCL/QVL: CPU, память, накопители, HBA, RAID, NIC, GPU и версии прошивок.

10. Типовые ошибки при выборе

- Покупка платы только по сокету. Сокет не гарантирует поддержку конкретного CPU.

- Игнорирование QVL памяти. Сервер может запускаться, но работать нестабильно под нагрузкой.

- Недостаток PCIe-линий. Устройства физически установлены, но работают в урезанном режиме.

- Несовместимость с корпусом. Плата подходит по размеру, но не совпадают стойки, airflow или расположение портов.

- Неправильный выбор для СХД. Недостаточно слотов для HBA, слабая сеть или отсутствие ECC.

- Отсутствие удаленного управления. Для серверов в стойке это усложняет обслуживание и восстановление после сбоев.

11. Когда нужна консультация инженера

Консультация особенно полезна, если сервер собирается под виртуализацию, СХД, GPU-нагрузку, базы данных, импортозамещение, нестандартное шасси или апгрейд существующей платформы. В таких сценариях ошибка выбора платы может потребовать замены корпуса, памяти, контроллеров или всей платформы.

Нужна проверка совместимости серверной платформы?

Подготовьте список процессоров, памяти, корпуса, накопителей, контроллеров, сетевых карт и задач сервера. Специалисты ANDPRO помогут проверить совместимость и подобрать конфигурацию под задачу.

Автор статьи: Сергей Коваль, koval@andpro.ru

Техническая проверка: Михаил Биркос, birkos@andpro.ru

12. Частые вопросы

Можно ли использовать обычную материнскую плату вместо серверной?

Можно, если речь идет о простом домашнем сервере или тестовой системе. Для корпоративных задач, виртуализации, СХД и работы 24/7 лучше использовать серверную плату с ECC-памятью, BMC/IPMI, проверенной совместимостью и поддержкой нужных интерфейсов.

Всегда ли серверной плате нужна ECC-память?

Для ответственных задач — да. ECC особенно важна для виртуализации, баз данных, файловых серверов, ZFS, СХД и длительной работы под нагрузкой. Конкретный тип ECC-памяти зависит от платформы.

Что важнее: сокет или чипсет?

Важны оба параметра. Сокет определяет физическую совместимость процессора, а чипсет и BIOS/UEFI — набор поддерживаемых функций, процессоров, памяти, интерфейсов и режимов работы.

Почему серверная плата может не подойти к корпусу того же размера?

Помимо размера важны монтажные отверстия, расположение разъемов питания, направление воздушного потока, высота радиаторов, доступность портов, поддержка райзеров и совместимость с бэкплейном корпуса.

Нужен ли IPMI/BMC для небольшого сервера?

Если сервер работает удаленно, в стойке или без постоянного физического доступа, IPMI/BMC сильно упрощает обслуживание. Для тестовой системы он не всегда обязателен, но для production-инфраструктуры крайне желателен.