Как войти в BIOS/UEFI и какие настройки проверить

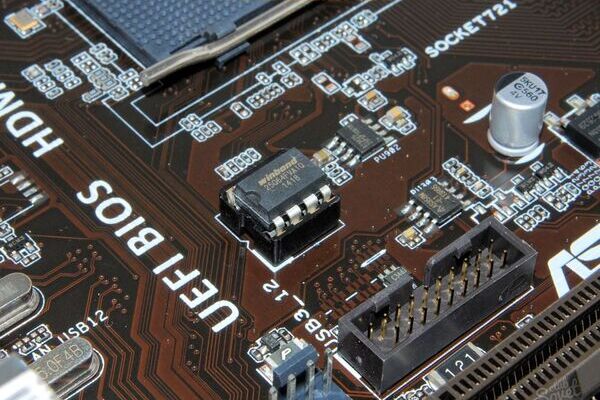

BIOS/UEFI — это базовая прошивка материнской платы, которая запускается до операционной системы и отвечает за инициализацию процессора, оперативной памяти, накопителей, видеокарты, вентиляторов, модулей безопасности и порядка загрузки. После сборки ПК, апгрейда, замены накопителя или установки Windows/Linux важно проверить несколько параметров UEFI, чтобы система работала стабильно и безопасно.

1. BIOS и UEFI: в чем разница

Термин BIOS часто используется по привычке, но на современных материнских платах почти всегда применяется UEFI — Unified Extensible Firmware Interface. UEFI выполняет те же базовые функции, что и классический BIOS, но поддерживает графический интерфейс, мышь, загрузку с GPT-дисков, Secure Boot, сетевые функции, профили настроек, обновление прошивки из интерфейса и расширенные средства диагностики.

В повседневной речи пользователи продолжают говорить «зайти в BIOS», хотя технически чаще всего речь идет именно о входе в UEFI Setup Utility.

| Параметр | Классический BIOS | Современный UEFI |

|---|---|---|

| Интерфейс | Текстовый, управление клавиатурой. | Графический или гибридный, часто поддерживает мышь. |

| Загрузка дисков | Ориентирован на MBR. | Поддерживает GPT и современные загрузчики. |

| Безопасность | Ограниченные функции. | Secure Boot, TPM, ключи загрузки, расширенная политика доверия. |

| Обновление | Часто требовало DOS-утилит или отдельной среды. | Обычно обновляется из встроенного EZ Flash / M-Flash / Q-Flash / Instant Flash. |

| Профили | Ограниченные возможности. | Сохранение профилей, экспорт на USB, мониторинг вентиляторов и напряжений. |

2. Как войти в BIOS/UEFI при включении компьютера

Самый универсальный способ — нажимать клавишу входа в UEFI сразу после включения питания, до начала загрузки операционной системы. На стационарных ПК чаще всего используется Delete, на ноутбуках — F2, но конкретная клавиша зависит от производителя платы или устройства.

| Производитель / платформа | Частые клавиши входа | Комментарий |

|---|---|---|

| ASUS | Delete, F2 | Delete чаще на десктопных платах, F2 часто на ноутбуках. |

| MSI | Delete | Для Boot Menu часто используется F11. |

| Gigabyte | Delete | Для Boot Menu часто используется F12. |

| ASRock | Delete, F2 | Instant Flash обычно доступен внутри UEFI. |

| Lenovo | F1, F2, Fn+F2, Novo Button | На части ноутбуков нужна клавиша Fn или отдельная кнопка Novo. |

| HP | Esc, затем F10 | Esc открывает стартовое меню, F10 — BIOS Setup. |

| Dell | F2 | Boot Menu обычно вызывается клавишей F12. |

| Acer | F2, Delete | На ноутбуках может потребоваться Fn+F2. |

3. Как войти в UEFI из Windows

Если система загружается слишком быстро и вы не успеваете нажать клавишу входа, используйте штатный способ Windows. Он особенно удобен на ноутбуках и ПК с включенной быстрой загрузкой.

- Откройте Параметры.

- Перейдите в раздел Система.

- Откройте Восстановление.

- В блоке Расширенный запуск нажмите Перезагрузить сейчас.

- Выберите Поиск и устранение неисправностей.

- Откройте Дополнительные параметры.

- Выберите Параметры встроенного ПО UEFI.

- Нажмите Перезагрузить.

После перезагрузки компьютер должен автоматически открыть интерфейс UEFI без необходимости нажимать Delete или F2.

4. Когда нужно заходить в BIOS/UEFI

Заходить в UEFI стоит не только при проблемах. После сборки или апгрейда компьютера нужно проверить, корректно ли определились процессор, память, накопители, вентиляторы и режим загрузки.

5. Что можно безопасно менять в UEFI

В UEFI есть параметры разного уровня риска. Часть настроек безопасна для большинства пользователей, а часть может привести к нестабильности, сбоям загрузки или потере доступа к системе до сброса CMOS.

| Настройка | Назначение | Риск |

|---|---|---|

| Boot Priority | Выбор устройства, с которого загружается система. | Низкий. Ошибка обычно исправляется возвратом правильного диска. |

| XMP / EXPO | Включение заводского профиля частоты и таймингов памяти. | Средний. Возможна нестабильность, если профиль не подходит контроллеру памяти. |

| Fan Control | Настройка кривых вентиляторов. | Низкий, если не занижать обороты слишком сильно. |

| TPM / fTPM / PTT | Модуль доверенной платформы для Windows 11, BitLocker и функций безопасности. | Средний. При BitLocker нужно учитывать ключи восстановления. |

| Secure Boot | Проверка доверенной загрузки ОС. | Средний. Может мешать загрузке неподписанных ОС и утилит. |

| CPU Voltage / Manual OC | Ручное изменение напряжений и частот процессора. | Высокий. Возможен перегрев, нестабильность и деградация компонентов. |

| Memory Timing Manual | Ручные тайминги оперативной памяти. | Высокий. Ошибки приводят к сбоям POST и ошибкам памяти. |

6. Как безопасно обновить BIOS/UEFI

Обновление UEFI может добавить поддержку новых процессоров, улучшить совместимость памяти, закрыть уязвимости, исправить ошибки загрузки или стабилизировать работу платформы. Но прошивку не стоит обновлять «просто так», если система работает стабильно и в описании новой версии нет важных для вас изменений.

Безопасный порядок обновления

- Уточните точную модель материнской платы и ревизию PCB.

- Скачайте прошивку только с официальной страницы производителя платы или устройства.

- Прочитайте описание версии BIOS: поддержка CPU, AGESA/ME, память, безопасность, исправления.

- Скопируйте файл прошивки на USB-накопитель, отформатированный в FAT32, если этого требует производитель.

- Зайдите в UEFI и запустите встроенную утилиту обновления.

- Дождитесь завершения прошивки и автоматической перезагрузки.

- После обновления загрузите Optimized Defaults.

- Заново включите XMP/EXPO, настройте порядок загрузки, вентиляторы, TPM/Secure Boot и другие нужные параметры.

| Производитель | Название встроенной утилиты | Типичный сценарий |

|---|---|---|

| ASUS | EZ Flash | Обновление из UEFI с USB-накопителя или через интернет в некоторых моделях. |

| MSI | M-Flash | Перезагрузка в режим прошивки и выбор файла BIOS на USB. |

| Gigabyte | Q-Flash | Обновление из UEFI; на части плат есть Q-Flash Plus без CPU/RAM. |

| ASRock | Instant Flash | Поиск подходящего файла прошивки на подключенном USB-накопителе. |

7. XMP и EXPO: как включить память на заявленной частоте

После установки оперативной памяти плата часто запускает ее на базовой безопасной частоте JEDEC, а не на частоте, указанной на упаковке комплекта. Для активации заявленных параметров используется профиль XMP у Intel-платформ и EXPO у AMD-платформ. На некоторых платах доступны оба типа профилей.

XMP/EXPO задает частоту, основные тайминги и напряжение памяти. Это заводской профиль, но он все равно является режимом выше базовой спецификации контроллера памяти, поэтому стабильность зависит от процессора, платы, количества модулей, объема памяти и версии BIOS.

Как включить XMP/EXPO

- Зайдите в UEFI.

- Найдите раздел AI Tweaker, OC, Extreme Tweaker, Overclocking или DRAM Settings.

- Выберите XMP Profile 1, EXPO Profile 1 или аналогичный профиль.

- Сохраните настройки через Save & Exit.

- После загрузки ОС проверьте стабильность памяти тестом и обычной рабочей нагрузкой.

8. Порядок загрузки: Boot Priority и Boot Menu

Boot Priority определяет, с какого устройства компьютер пытается загрузить операционную систему. Это важно при установке Windows или Linux, переносе системы на новый SSD, подключении нескольких накопителей и восстановлении загрузчика.

Для установки ОС обычно лучше использовать Boot Menu: выбрать USB-накопитель один раз, установить систему, а затем оставить первым устройством системный SSD или Windows Boot Manager.

9. Secure Boot, TPM и Windows 11

Современные системы используют функции доверенной загрузки. Secure Boot проверяет подпись загрузчика, а TPM хранит криптографические ключи и используется Windows 11, BitLocker и рядом корпоративных политик безопасности.

| Параметр | Где встречается | Когда включать |

|---|---|---|

| Secure Boot | Boot / Security | Для Windows 11, корпоративной безопасности и защиты от неподписанных загрузчиков. |

| TPM 2.0 | Security / Trusted Computing | Для Windows 11, BitLocker, аппаратных ключей и политик доверенной платформы. |

| Intel PTT | Security / PCH-FW Configuration | Встроенная реализация TPM на Intel-платформах. |

| AMD fTPM | Security / AMD fTPM | Встроенная реализация TPM на AMD-платформах. |

| CSM | Boot | Для современных систем обычно отключают, чтобы использовать чистый UEFI-режим. |

10. Виртуализация, Resizable BAR и другие полезные настройки

Некоторые параметры UEFI стоит проверить сразу после сборки компьютера, особенно если система используется для виртуальных машин, игр, рабочих станций или профессиональных приложений.

| Настройка | Назначение | Кому нужна |

|---|---|---|

| Intel VT-x / AMD SVM | Аппаратная виртуализация CPU. | VirtualBox, VMware, Hyper-V, Docker, WSL, Proxmox. |

| VT-d / IOMMU | Проброс устройств и изоляция DMA. | Виртуализация, серверные сценарии, PCIe passthrough. |

| Resizable BAR | Расширенный доступ CPU к видеопамяти GPU. | Игровые ПК и рабочие станции с современными видеокартами. |

| Above 4G Decoding | Адресация PCIe-устройств за пределами 4 ГБ. | Много GPU, HBA, сетевые карты, Resizable BAR. |

| Fan Curve | Кривые вентиляторов по температуре. | Все системы, особенно тихие ПК и рабочие станции. |

| SATA Mode | Режим контроллера SATA/AHCI/RAID. | Системы с SATA SSD/HDD или RAID-массивами. |

11. Что проверить после сборки или апгрейда

После первого запуска компьютера не стоит сразу устанавливать все программы и переносить данные. Сначала проверьте базовую аппаратную конфигурацию в UEFI.

12. Что делать, если после настройки ПК не стартует

Чаще всего проблемы после изменения UEFI связаны с памятью, ручным разгоном, некорректным режимом загрузки или слишком агрессивными параметрами питания. Если компьютер не проходит POST или уходит в циклическую перезагрузку, нужно вернуть настройки к безопасным.

- Выключите компьютер и отключите питание.

- Подождите 30–60 секунд.

- Используйте кнопку Clear CMOS, перемычку CLR_CMOS или извлеките батарейку CR2032 на несколько минут.

- Запустите систему и войдите в UEFI.

- Загрузите Optimized Defaults.

- Включайте XMP/EXPO и другие параметры по одному, проверяя стабильность после каждого изменения.

13. Часто задаваемые вопросы

Какая клавиша открывает BIOS/UEFI?

На большинстве десктопных материнских плат используется Delete, на многих ноутбуках — F2. У HP часто используется Esc, затем F10; у Dell — F2; у Lenovo — F1, F2 или кнопка Novo.

Можно ли обновлять BIOS, если компьютер работает нормально?

Можно, но не всегда нужно. Обновление оправдано, если новая версия добавляет поддержку процессора, улучшает совместимость памяти, исправляет важные ошибки или закрывает уязвимости. Если система стабильна, а описание новой версии не содержит нужных изменений, обновление можно отложить.

Почему после включения XMP/EXPO компьютер не загружается?

Профиль памяти может быть слишком тяжелым для конкретного контроллера памяти, комплекта модулей или версии BIOS. Помогают обновление UEFI, снижение частоты памяти, увеличение задержек или выбор более консервативного профиля.

Что выбрать в Boot Priority после установки Windows?

Обычно первым должен стоять Windows Boot Manager на системном SSD. Не всегда нужно выбирать сам физический диск: в UEFI-системах загрузчик часто отображается именно как Windows Boot Manager.

Нужно ли включать Secure Boot?

Для Windows 11 и корпоративных требований безопасности Secure Boot обычно стоит включить. Но при установке некоторых Linux-дистрибутивов, диагностических утилит или неподписанных загрузчиков Secure Boot может потребовать дополнительной настройки или временного отключения.

Что такое TPM, Intel PTT и AMD fTPM?

TPM — модуль доверенной платформы. Intel PTT и AMD fTPM — встроенные реализации TPM в современных платформах. Они используются Windows 11, BitLocker и механизмами защиты ключей.

Что делать, если после изменения BIOS появился черный экран?

Отключите питание и выполните Clear CMOS. После сброса загрузите оптимальные настройки, затем включайте нужные параметры постепенно. Чаще всего проблема связана с памятью, режимом загрузки или ручными настройками разгона.

14. Итог

UEFI — это не только меню для выбора загрузочной флешки. Это центр базовой конфигурации компьютера: память, накопители, безопасность, вентиляторы, виртуализация, порядок загрузки и обновления прошивки. Большинство пользователей может безопасно работать с базовыми параметрами, если меняет настройки последовательно и понимает назначение каждого пункта.

После сборки или апгрейда важно проверить распознавание компонентов, включить корректный профиль памяти, настроить загрузку с системного SSD, убедиться в работе TPM/Secure Boot и сохранить профиль настроек. Ручные напряжения, агрессивный разгон и тонкие тайминги памяти лучше менять только при понимании рисков и наличии времени на тестирование стабильности.

Автор статьи: Сергей Коваль. Технический аудит и экспертная оценка: Михаил Биркос.